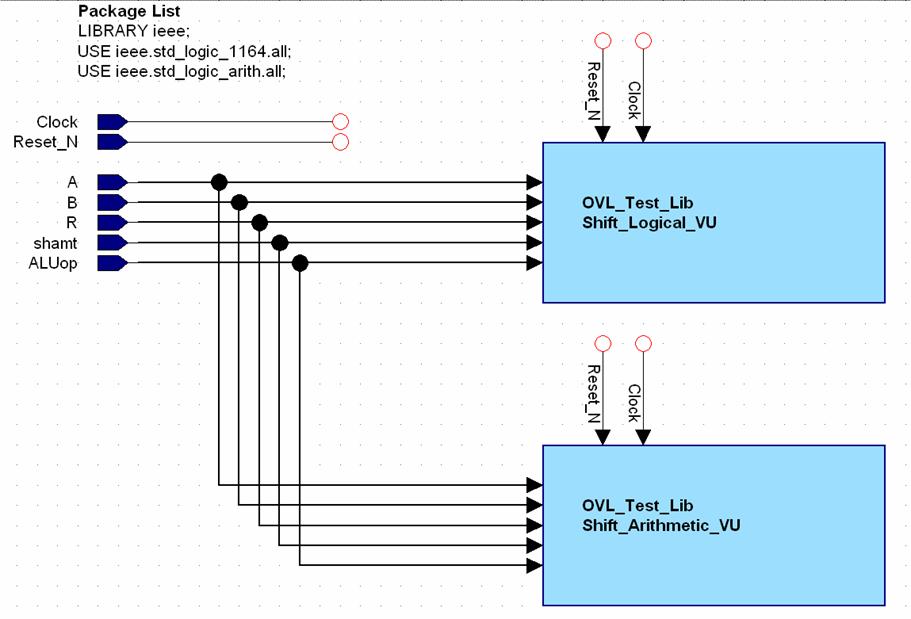

Verification of Shift Operations

The verification

units for the shift operation are similar to the comparisons in that they also

need to be separated into signed (Arithmetic Shift) and unsigned (Logical

Shift) entities. The assertions for Left

and Right Logical Shifts are as follows:

antecedent_expr1

<= true when ALUop="1110" else false;

consequent_expr1

<= true when (SHR(A,shamt)) = R else false;

antecedent_expr2

<= true when ALUop="1100" else false;

consequent_expr2

<= true when (SHL(A,shamt)) = R else false;

SHR and SHL are std_logic_vector logical shift

operations defined in the STD_LOGIC_UNSIGNED package, which once again needs to

be added to the package list within the Shift_Logical verification entity. Repeat the above for the Arithmetic shift,

but use the signed shift operation defined in the STD_LOGIC_SIGNED package.