Verification of Logic Operations

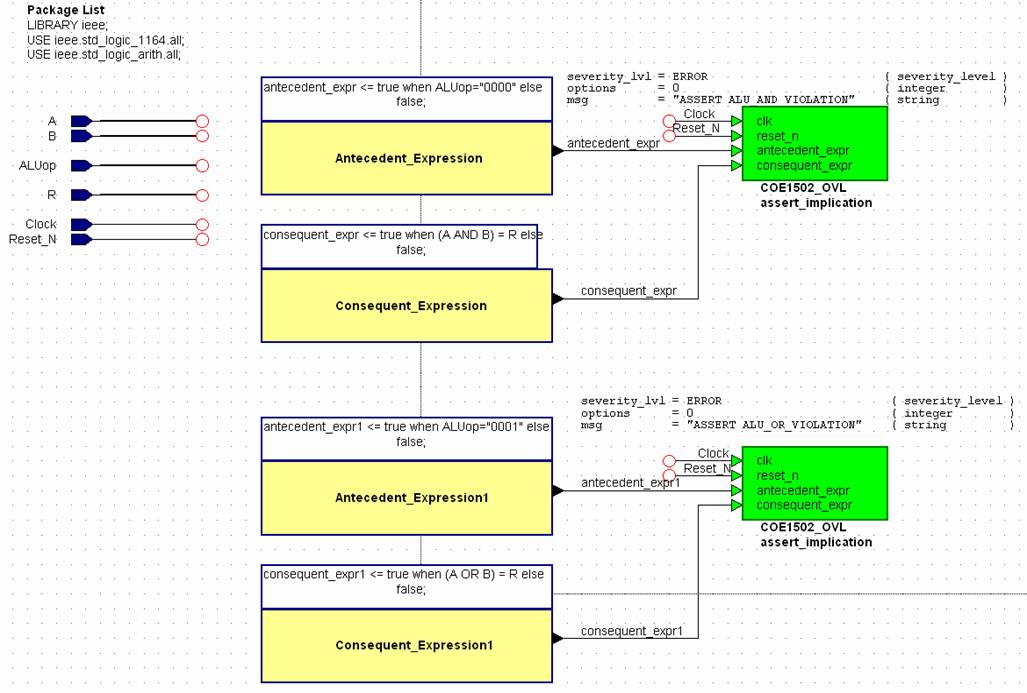

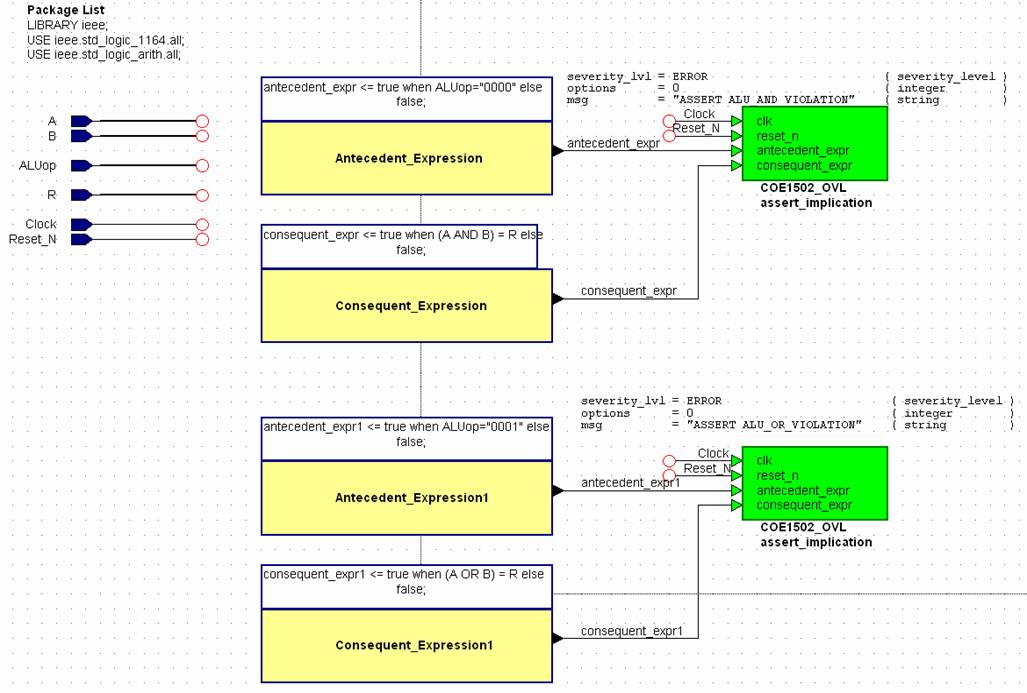

The first verification unit we will construct will be for the logical

operations. We will only make use of one

component from the Open Verification Library, assert_implication. Read its description from the documentation (Assert_Implication).

We will use a comparison of ALUop as the antecedent expression; this

identifies which operation we are verifying. A comparison of the returned

result ( R ) to the expected result (For the case of ALUop =”0000” we expect a

result of A AND B ) is used as the

consequent expression. If the antecedent

expression is true but the consequent expression evaluates false, an error will

be reported to the simulator. We have

the option of writing what that error message will be and its severity level

(Right Click on Component à Object Properties à Generics).

Use severity_lvl = ERROR, any level higher than this will cause the

simulator to halt operation when errors are detected.

Figure 6.

Shown above are the assertions for the AND and OR operations, you will

also have to include assertions for the other two logical operators in your

testbench.

Click here to proceed