Verification of Comparison

Operations

Verification of

the comparison operators has to be handled differently than the logical

operations. The result can now differ

depending on whether the operands are considered to be signed or unsigned

numbers. For both cases however, the

assertions will look identical ( Except for

ALUop ):

--Antecedent Expression

antecedent_expr <= true when ALUop="1011" else false;

--Consequent Expression

consequent_expr <= true when ( (

A < B) AND (R =

X"0000_0000_0000_0001" )) OR ( ( A >= B) AND(R=

X"0000_0000_0000_0000"

)) else false;

So how do we differentiate

between signed and unsigned operands in our design? The VHDL operations ‘<’ and ‘>=’ for std_logic_vectors are defined inside of the IEEE library

and we can choose which definition to use.

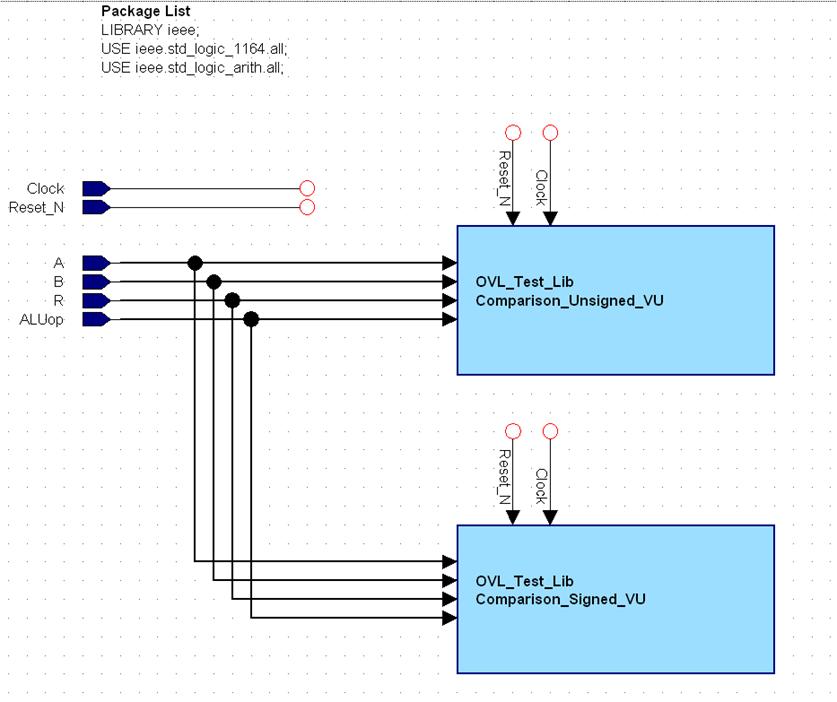

The first step in doing so is to split up the signed and unsigned

operations into two separate entities as shown in Figure 7. This has to be done because it is not

possible to have two definitions for the same operator, ‘< signed’ and ‘<

unsigned’, defined within the same scope.

Figure 7.

Descend into the

Comparison_Unsigned entity and add the assertion for

it that is shown above. Next,

double-click on the Package List in the top left-hand corner of the schematic

window.

Figure 8.

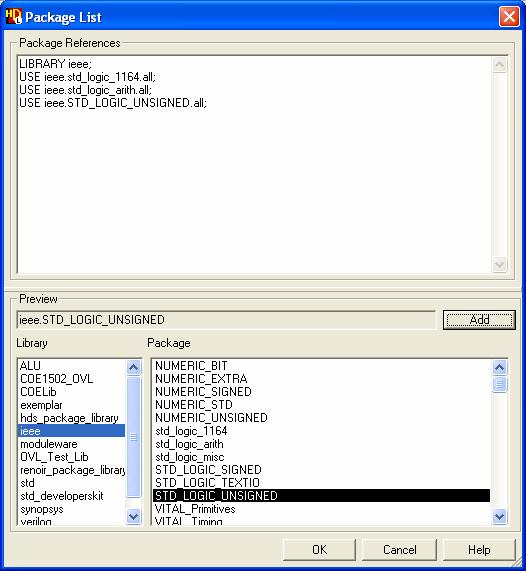

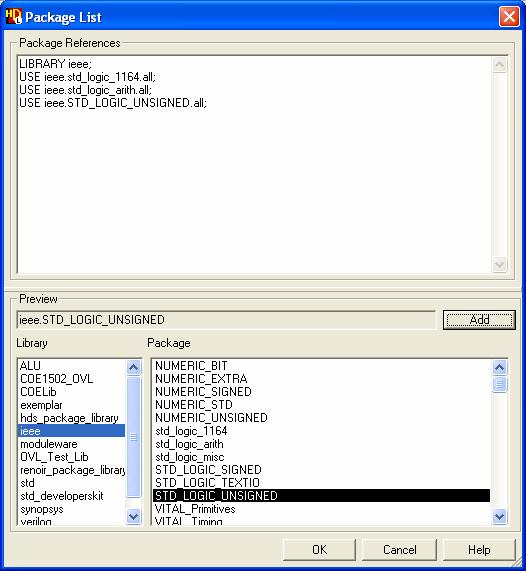

When you do so,

you should see the following pop-up window.

Add the STD_LOGIC_UNSIGNED package to the Package list by selecting it

(Located within the IEEE library) and clicking the Add button. Your screen should look like the below figure

after it has been added. The ‘<’

operation defined within this package interprets the operands as unsigned

values. You can look at the definitions

for yourself by opening up the IEEE library from HDL Design Manager and

browsing through the package definition for STD_LOGIC_UNSIGNED.

Figure 9.

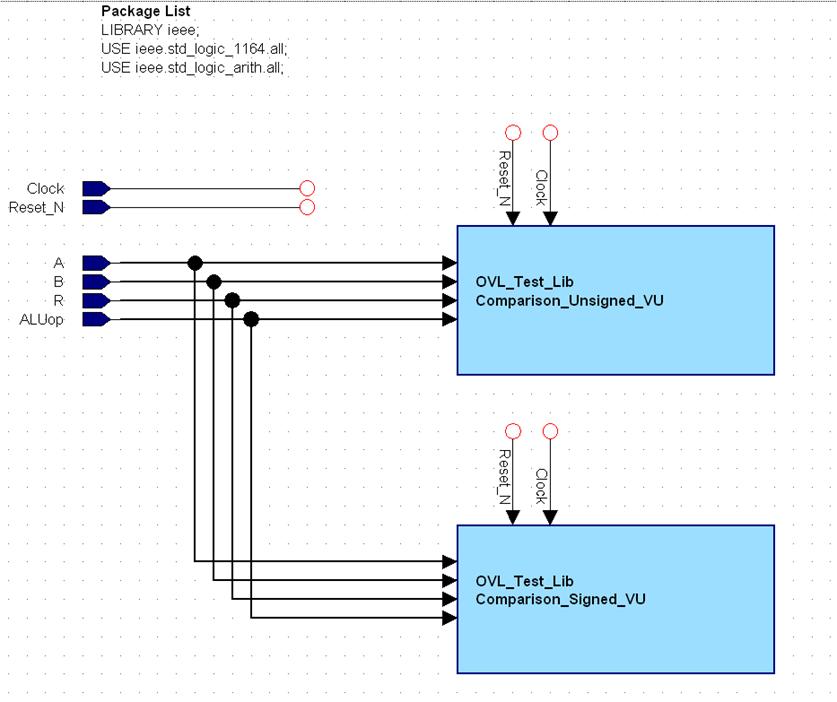

Repeat all of

the above for the Signed Comparison entity, except this time add the

STD_LOGIC_SIGNED package to the package list.

The operations within this package interpret the operands as signed

two’s complement numbers.

Click here to proceed