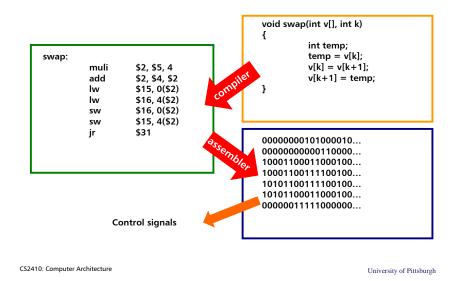

#### C to binary to electrical signals

#### **CS2410: Computer Architecture**

#### Instruction set architecture principles and examples

#### Sangyeun Cho

Computer Science Department University of Pittsburgh

ISA?

#### ISA components:

- Data types supported (e.g., bytes, half words, words-signed, unsigned)

- Registers as a storage of data or information

- General registers: e.g., R0~R7

- Special registers: e.g., PSR (processor status register), return address from exception, ...

- Processor modes

- User mode, privileged mode, …

- Register view in different modes

- Instruction definitions

- Basic semantics: e.g., add, multiply

- Exception behaviors: e.g., load misaligned access, TLB miss, …

- Some instructions may behave differently in different modes

- Some instructions are not available in user mode (e.g., privileged instructions)

- ...

- ABI (application binary interface)

- ≠ ISA

- · Defines low-level binary interface between an application and the OS

- Calling convention

System call mechanism

- System call mecha

- Binary format, …

University of Pittsburgh

## **ISA design considerations**

- Target application

- General-purpose processor

- Application-specific processor

- Roadmap

- Properties generally considered desirable

- Completeness

- Orthogonality

- Regularity and simplicity

- Compactness–code size

- Ease of programming

- Ease of implementation

- Ease of extension

#### **Machine instructions**

- Operation "what" to do?

- How many operations?

- What kind of operations?

- Early processors omitted "multiply"

- Floating-point operations were also absent

- Operands what do we operate on?

- How many operands?

- Where are they stored?

- How to specify?

- Format

- Fixed N byte or variable size

- What are necessary subfields?

- How are subfields laid out?

CS2410: Computer Architecture

University of Pittsburgh

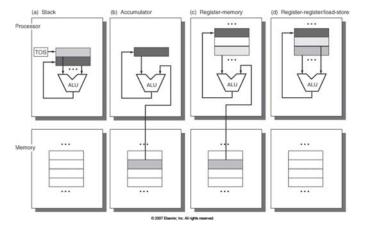

### **Operand location**

- Stack

- Implicit use data on the top of the stack

- Accumulator

- Implicit there is one accumulator

- Register

- Memory

CS2410: Computer Architecture

University of Pittsburgh

#### **Operand location**

## Number of operands

- Stack

0 address

add

tos ← tos + next

Accumulator

1 address

add A

acc ← acc + mem[A]

Register/memory

2 addresses

add A B

A ← A + B

3 addresses

add A B C

A ← B + C

- Load store architectures disallow operation and memory access in a single instruction

CS2410: Computer Architecture

#### Sample code sequence

#### C = A + B

| Stack | ¢         |         | nulator | Regist<br>(regist | er<br>er-memory) | Regist | er (load-store) |

|-------|-----------|---------|---------|-------------------|------------------|--------|-----------------|

| Push  | A         | Load    | A       | Load              | R1,A             | Load   | R1,A            |

| Push  | В         | Add     | В       | Add               | R3,R1,B          | Load   | R2,B            |

| Add   | (strain)) | Store   | C       | Store             | R3,C             | Add    | R3,R1,R2        |

| Рор   | С         | 1010326 |         | 202.100           |                  | Store  | R3,C            |

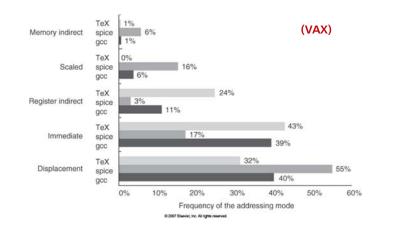

## Specifying operands

- "Addressing mode"

- Register direct add R1, R2, R3

- Immediate add R1, R1, #1

- Memory

•

•

- Direct (absolute)

- Register indirect

- Memory indirect

- Displacement

- Indexed

- Scaled

CS2410: Computer Architecture

Auto-increment/decrement

University of Pittsburgh

load R1, @(10000)

load R1, @(R2)

load R1, @((R2))

load R1, @(R2+100)

load R1, @(R2+R3×d+100)

load R1, @(R2+R3)

load R1, @(R2+/-)

CS2410: Computer Architecture

#### Usage of addressing modes

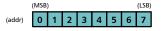

#### **Endian-ness and data alignment**

- Big endian vs. little endian

- Defines byte ordering inside a larger data type stored in memory

- (addr) 7 6 5 4 3 2 1 0

- Alignment

- Data A is aligned if (addr(A) % sizeof(A) == 0) is true

- What is the implication on hardware implementation (esp. memory system)?

University of Pittsburgh

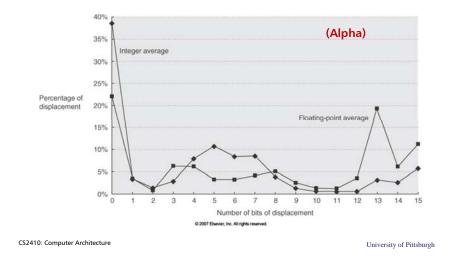

# **Displacement size**

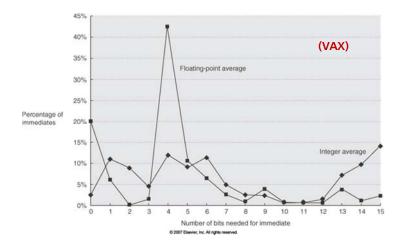

#### **Immediate size**

CS2410: Computer Architecture

University of Pittsburgh

## **Operations**

- Arithmetic

- add, sub, mul, div, ...

- Logical

- and, or, xor, not, ...

- Shift

- shift-left, shift-right, shift-right-arithmetic, ...

- Memory access

- load, store, prefetch, ...

- Control

- branches, jumps, procedure call/return, ...

- System-related

- trap, break, ...

University of Pittsburgh

## **Frequent operations**

| Rank  | 80x86 instruction      | Integer average<br>(% total executed) |

|-------|------------------------|---------------------------------------|

| 1     | load                   | 22%                                   |

| 2     | conditional branch     | 20%                                   |

| 3     | compare                | 16%                                   |

| 4     | store                  | 12%                                   |

| 5     | add                    | 8%                                    |

| 6     | and                    | 6%                                    |

| 7     | sub                    | 5%                                    |

| 8     | move register-register | 4%                                    |

| 9     | call                   | 1%                                    |

| 10    | return                 | 1%                                    |

| Total |                        | 96%                                   |

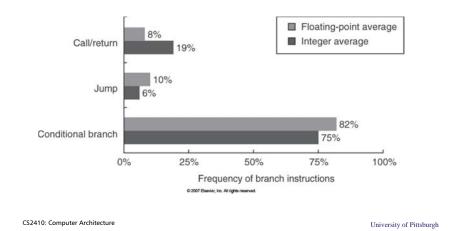

## **Control flow instructions**

#### **Operands of control flow inst.**

- Target description

- Instruction with an immediate value

- PC-relative or absolute

- In register

- Typically absolute

- Condition description

- Condition bit (zero, carry, overflow, ...)

- sub R1, R2, R3; bz LABEL

- Condition register

- cmp R1, R2, R3; bgtz R1, LABEL

- Compare-and-branch

- bgt R1, R2, LABEL

CS2410: Computer Architecture

University of Pittsburgh

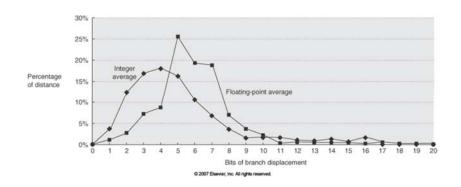

#### **Branch distance**

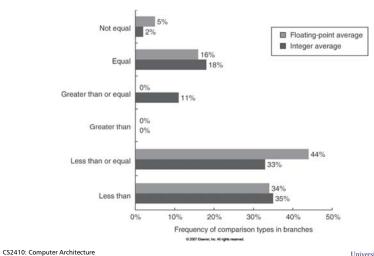

## **Comparison types**

University of Pittsburgh

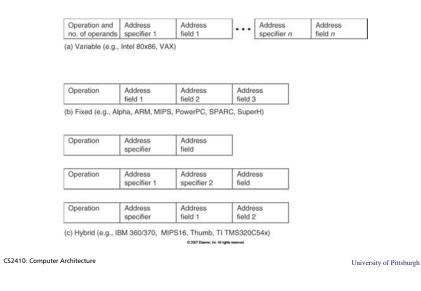

#### **Instruction format**

### How to help compiler writers

- At least 16 GPRs

- Provide regularity

- Orthogonality

- No restrictions on register usage

- Provide primitives, not solutions

- e.g., HLL-like operations

- Simplify trade-offs in alternatives

- Provide instructions that bind constants

CS2410: Computer Architecture

University of Pittsburgh

## **MIPS** example

- Thirty-two 32-bit GPR

- R0 wired to 0

- Separate 32/16 SP/DP (single-/doubleprecision) FP registers

- Byte/half/word/dword, SP/DP FP data types

- Immediate and displacement addressing modes

- 32-bit fixed instruction encoding

# **ARM** example

- Sixteen 32-bit GPR

- R14 is link register

- R15 is PC

- Different CPU modes have different register view

- Immediate and displacement addressing modes

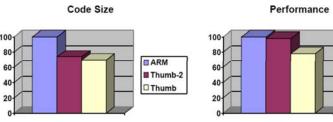

- "Thumb" mode supports 16-bit instruction encoding

|            | -      |            | Privileg        | ed modes- |           |                |  |  |  |  |  |  |  |  |  |

|------------|--------|------------|-----------------|-----------|-----------|----------------|--|--|--|--|--|--|--|--|--|

|            |        | ·          | Exception modes |           |           |                |  |  |  |  |  |  |  |  |  |

| User       | System | Supervisor | Abort           | Undefined | Interrupt | Fast interrupt |  |  |  |  |  |  |  |  |  |

| RD         | RO     | RO         | PD.             | R0        | R2        | R0             |  |  |  |  |  |  |  |  |  |

| <b>P</b> H | RI     | 81         | 81              | 81        | 81        | 81             |  |  |  |  |  |  |  |  |  |

| P2         | 82     | R2         | P2              | R2        | R2        | R2             |  |  |  |  |  |  |  |  |  |

| PD         | P(3    | 83         | 83              | 83        | R3        | R3             |  |  |  |  |  |  |  |  |  |

| PH         | Ri     | 84         | Pi4             | 64        | 64        | 84             |  |  |  |  |  |  |  |  |  |

| P6         | P5     | 95         | P5              | R5        | RS        | RS             |  |  |  |  |  |  |  |  |  |

| 76         | FI6    | 26         | Pit             | PH.       | RE        | 86             |  |  |  |  |  |  |  |  |  |

| 10         | RT     | 87         | 87              | 87        | R7        | R/             |  |  |  |  |  |  |  |  |  |

| 78         | P8     | PR.        | 76              | Pit .     | R8        | MA             |  |  |  |  |  |  |  |  |  |

| PU .       | 89     | 10         | 10              | 89        | 10        | A 10.14        |  |  |  |  |  |  |  |  |  |

| Pris       | R10    | #10        | #10             | #10       | R10       | R10,84         |  |  |  |  |  |  |  |  |  |

| #t11       | R115   | R115       | #11             | 815       | 811       | R11.54         |  |  |  |  |  |  |  |  |  |

| P112       | mt2    | R12        | P12             | R12       | R12       | A RELAU        |  |  |  |  |  |  |  |  |  |

| Rt3        | R13    | Rt3, ave   | R13, MI         | RT3, and  | Rt2,m     | R12,84         |  |  |  |  |  |  |  |  |  |

| 814        | R14    | ANA.me     | R14, at         | R14, and  | Ris.iq    | A MILEO        |  |  |  |  |  |  |  |  |  |

| PC         | PC     | PC         | PC              | PC        | PC        | PC             |  |  |  |  |  |  |  |  |  |

| CPSR       | CPSR   | OPSIA      | CPSR            | OPER      | OPER      | OPER           |  |  |  |  |  |  |  |  |  |

|            |        | SPER. M    | SPSR air        | SPSR.und  | S. SPSR.M | SPSR.M         |  |  |  |  |  |  |  |  |  |

University of Pittsburgh

CS2410: Computer Architecture

#### **ARM** example

|                                                             |          | 27 | 28 | : 1 | 24 | 23  | ::  | :11  | 20 | 13 | 18.17 | 1.0 |   | 10 | 11  | 1.3   |    |      |      |     |      | ,    |       |     | 4    |     | 2   |      |   |

|-------------------------------------------------------------|----------|----|----|-----|----|-----|-----|------|----|----|-------|-----|---|----|-----|-------|----|------|------|-----|------|------|-------|-----|------|-----|-----|------|---|

| Data processing immediate shift                             | cond [1] | 0  | 0  | 0   | 4  | pci | d   | ÷.,  | s  |    | Rn    |     | Γ | R  | d.  |       |    | shi  |      | mo  | unt  |      | shit  | ŧ   | 0    |     | R   | n    |   |

| Miscellareous instructions:<br>See Figure 3-3               | cond [1] | 0  | 0  | 0   | 1  | 0   | *   | *    | 0  | ×  | * *   | .*  | × | *  | ×   | *     | *  | ,    |      | •   |      | ,    | x :   | -   | 0    | x   | *   | ×    | × |

| Data processing register shift (2)                          | cond [1] | 0  | 0  | 0   | 1  | po  | ođ  | ,    | s  | Г  | Rn    |     | Г | ş  | u.  |       | Г  |      | Rs   |     | T    | 1    | shi   | 1   | 1    |     | R   |      |   |

| Miscellaneous instructions:<br>See Figure 3-3               | cond [1] | 0  | 0  | 0   | 1  | 0   | ×   | ×    | 0  | ×  | к.х   | *   | × | ×  | ,   | ×     | ×  | ,    | 0    | 0   | -    | 7    | x.    | (   | 1    | ×   | x   | ×    | x |

| Multiplies, extra load/stores:<br>See Figure 3-2            | cond [1] | 0  | 0  | 0   | ×  |     | *   | *    | ×  | ×  | 1.1   | ×   | × | ×  | x   | ×     | ×  | 5    | ( )  | 0   | 1    |      | x :   | ¢   | 1    | x   | ×   | ×    | × |

| Data processing immediate [2]                               | cond [1] | 0  | 0  | 1   | 1  | spo | od  | ,    | s  | Γ  | Rn    |     | Г | 5  | ы   |       | Γ  | =    | * 28 | *   | Τ    |      | )     | -   | -    | dat | ÷   |      |   |

| Undefined instruction [0]                                   | cond [1] | 0  | 0  | 1   | 1  | 0   | x   | 0    | 0  | ×  | х х   | ×   | × | ×  | ×   | ×     | *  | 2    |      | × . | x :  | ¢    | ×     | ¢   | ×    | x   | ×   | ×    | × |

| Move immediate to status register                           | cond [1] | 0  | 0  | 1   | 1  | 0   | R   | 1    | 0  | Γ  | Mask  |     |   | SI | 90  |       | Γ  | 1    | dad  |     | Τ    |      | 1     | in  | 10   | dal | •   |      |   |

| Loadistore immediate offset                                 | cond [1] | 0  | 1  | 0   | P  | U   | в   | w    | L  | Γ  | Rn    |     | Γ | 8  | đ   |       | Γ  |      |      |     |      |      | ed    | ion |      |     |     |      |   |

| Loadistore register offset                                  | cond [1] | 0  | 1  | 1   | P  | υ   | B   | w    | L  |    | Rn    |     |   | R  | d   |       | ,  | N    | 1.0  | mo  | urt  | Ι    | shift | 1   | 0    | ŝ   | R   | 10   |   |

| Undefined instruction                                       | cond [1] | 0  | 1  | 1   | ×  | ×   | ×   | ×    | ×  | ×  | хх    | ×   | × | ×  | ×   | ×     | ×  | 1    | G    | o   | 0    | ¢.   | ×     | ×   | 1    | ×   | ×   | ×    | x |

| Undefined instruction [4,7]                                 | 1.1.1.1  | Ó  | ×  | ×   | ×  | ×   | ×   | ×    | ×  | ×  | * *   | ×   | × | ×  | ×   | ×     | ×  |      | ċ    | í.) | 0    | ć    | ×.    | ×   | ×    | ×   | x   | x    | x |

| Loadistore multiple                                         | cond [1] | 1  | 0  | 0   | P  | U   | s   | w    | L  | Γ  | Rn    |     | Γ |    |     |       |    |      | 1    | egi | 1.10 | r lä | st    |     |      |     |     |      |   |

| Undefined instruction (4)                                   | 1 1 1 1  | 1  | 0  | 0   | ×  | ×   | *   | *    | ×  |    | * *   | ×   | * | ×  | *   | ×     | *  |      | 0    |     | •    |      | × :   | к.  | ×    | ×   | ×   | ×    | × |

| Branch and branch with link                                 | cond [1] | 1  | 0  | 1   | L  |     |     |      |    |    |       |     |   |    | 24  | F bil | of | To e | 4    |     |      |      |       |     |      |     |     |      |   |

| Branch and branch with link<br>and change to Thumb [4]      | 1.1.1.1  | 1  | 0  | 1   | н  |     |     |      |    |    |       |     |   |    | 24  | i bi  | of | t) e | 1    |     |      |      |       |     |      |     |     |      |   |

| Coprocessor load/store and double<br>register transfers (6) | cond (5) | 1  | 1  | 0   | P  | U   | N   | w    | L  | Γ  | Rn    |     | Γ | c  | Rid |       | -  | cp,  | m    | m   | Τ    |      | 1     | 5-0 | it ( | the | et. |      |   |

| Coprocessor data processing                                 | cond [5] | 1  | ۲  | 1   | 0  | .0  | po  | de   | 1  | Γ  | CRn   |     | Γ | c  | Rđ  |       | 1  | cp,  | ,14  | m   | 0    | p0   | ode   | 2   | 0    |     | c   | èm   |   |

| Coprocessor register transfers                              | cond [5] | 1  | 1  | 1   | 0  | op  | 000 | le 1 | L  |    | CRn   |     |   | F  | d   |       |    | cp,  | ,nu  | e1. | 0    | po   | ode   | 2   | 1    |     | Ø   | len. |   |

| Software interrupt                                          | cond [1] | 1  | 1  | i   | 1  |     |     |      |    |    |       |     |   |    |     | á n   | um | be   | i    |     |      |      |       |     |      |     |     |      |   |

| Undefined instruction [4]                                   | 1 1 1 1  | 1  | ł. | 1   | 1  | ×   | ×   | ×    |    | ×  | * *   | ×   |   |    |     | ×     |    |      |      |     |      | ċ    |       |     | *    | x   | ×   | ×    | × |

CS2410: Computer Architecture

University of Pittsburgh

#### ARM example, cont'd

**The Condition Field**

| 31 28 27 |                                   |                                                             |

|----------|-----------------------------------|-------------------------------------------------------------|

| cond     |                                   |                                                             |

|          | Condition Field                   |                                                             |

|          | 0000 = EQ (equal)                 | - Z set                                                     |

|          | 0001 = NE (not equal)             | - Z clear                                                   |

|          | 0010 = CS (unsigned higher or sam | ne) - Ciset                                                 |

|          | 0011 = CC (unsigned lower)        | - C clear                                                   |

|          | 0100 = MI (negative)              | - N set                                                     |

|          | 0101 = PL (positive or zero)      | - N clear                                                   |

|          | 0110 = VS (overflow)              | - V set                                                     |

|          | 0111 = VC (no overflow)           | - V clear                                                   |

|          | 1000 = HI (unsigned higher)       | - C set and Z clear                                         |

|          | 1001 = LS (unsigned lower or same | e) - C clear or Z set                                       |

|          | 1010 = GE (greater or equal)      | <ul> <li>N set and V set, or N clear and V clear</li> </ul> |

|          | 1011 = LT (less than)             | <ul> <li>N set and V clear, or N clear and V set</li> </ul> |

|          | 1100 = GT (greater than)          | - Z clear, and either N set and Vset, or N clear and V clea |

|          | 1101 = LE (less than or equal)    | - Z set, or N set and V clear, or N clear and V set         |

|          | 1101 = AL                         | - always                                                    |

|          | 1111 = NV                         | - never                                                     |

CS2410: Computer Architecture

University of Pittsburgh

#### **ARM** example

(Phelan, '03)

## **Summary**

- Instruction set design requires understanding of

- Application

- Roadmap •

- Properties affecting hardware implementation

- Properties affecting software design (e.g., application, compiler, ...)

- Binary compatibility has been a key market driver

- Legacy binaries

- Dynamic binary translation technology may weaken the • dependency

Thumb